4月学习自学内容总结

PCIe,基本搞懂了物理层的一些技术点知识,先上自认为比较好的视频教程(Youtube需翻墙 https://www.youtube.com/watch?v=EHkuzkNWXFk&t=2289s)

再呈上自认为讲的比较清的博客http://blog.chinaaet.com/justlxy/p/5100053481

对于硬件设计来说,以下几点比较重要值得参考

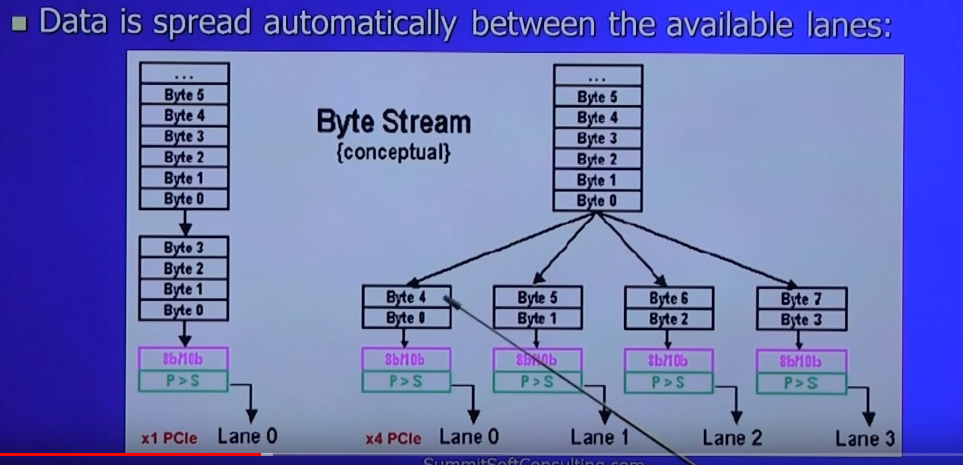

Lane之间不用等长:Intel主导下的PCIe这个设计标准对硬件工程师是大大的友好;主要是靠芯片内部增加FIFO,同时再上电后先进行建链训练,找出每条lane之前的到达时间差异,补偿进去,实现Lane之前不需要等长

差分对PN可交换Lane顺序可翻转:这一点也是通过训练时学习得出连接关系,这使得再穿过孔,直角连接器等设计的时候,lane互联走线设计不需要大量的过孔来调整线序。

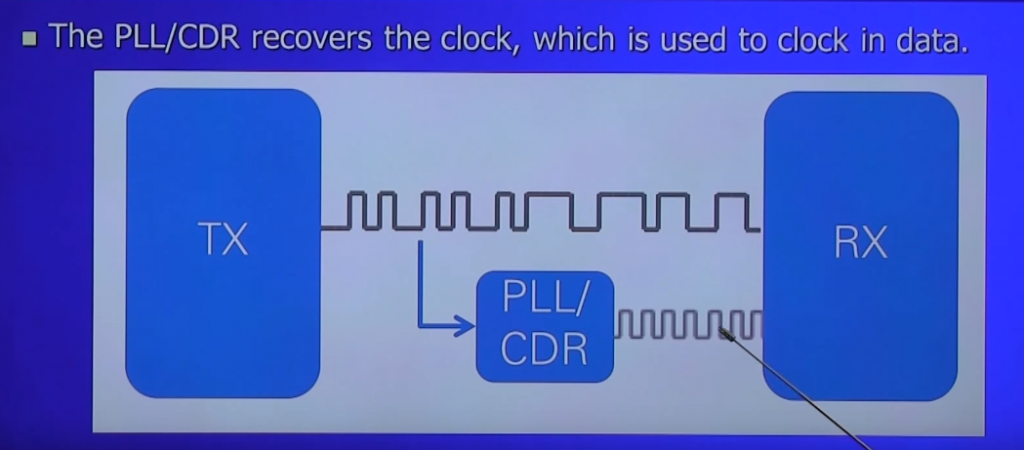

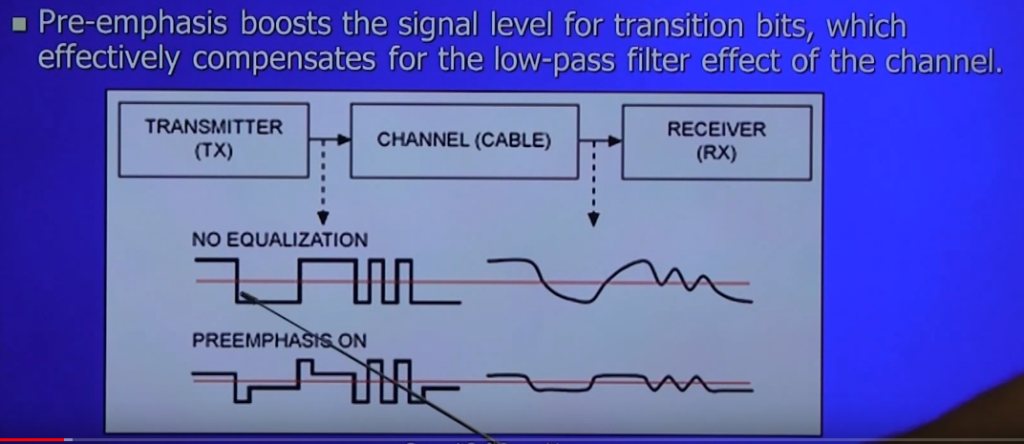

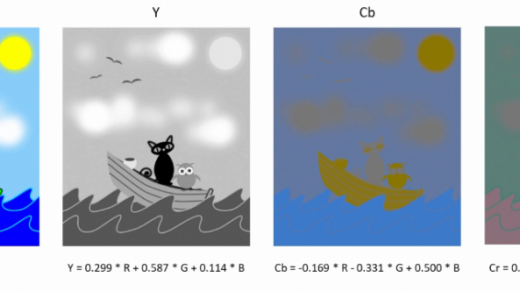

CDR时钟恢复技术:核心思想是通过8b/10b编码,把原本应该是随机传输的数据变成大概率经常0/1跳变的数据(用浪费2/10数据来提高交流分量),使得电路能从中提取出变化的频率,即时钟。举例说明,如果传输的数据哪怕所有bit都是1,通过8b/10b编码后,会也会转成01交替的数据,让接收端很容易提取出交替频率(时钟)

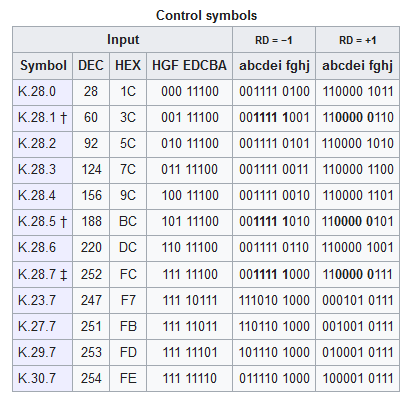

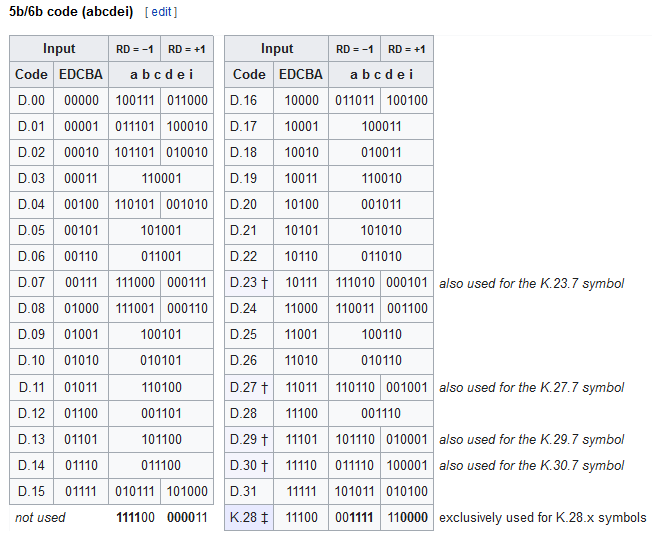

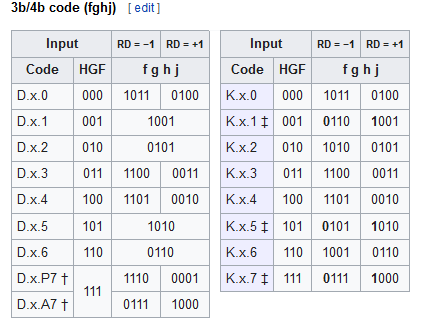

8b/10b编码技术 :通过浪费的20%,将1byte256个数字组合扩展成1024个数字组合,将0或者1连续的数组合去掉重新映射到分散开的其他组合上,实现直流平衡,同时一些控制字符也插入进来,如建立链接时用的K28.5等控制字符, 下面链接很详细介绍了规则,https://en.wikipedia.org/wiki/8b/10b_encoding;

值得注意的是PCIe3.0后不再用8b10B而用128b/130b,原因是8b/10b利用率太低,这也是为什么PCIe2虽然时5GT/s的速率但只有4Gbps的数据带宽,PCIe3.0使用 128b/130b 由于利用率的提高,使得编码自身不足以打乱连续的数据,所以伪随机扰码(发送和接收都有同样的种子和钥匙)必须增加以实现直流平衡,但理论上仍然存在一组数据,能和伪随机扰码一起变成一串0或1,使得其直流失恒,卡死PCIe,不知道我的这个理解是否正确

另外一些细节截图加强记忆

近期评论